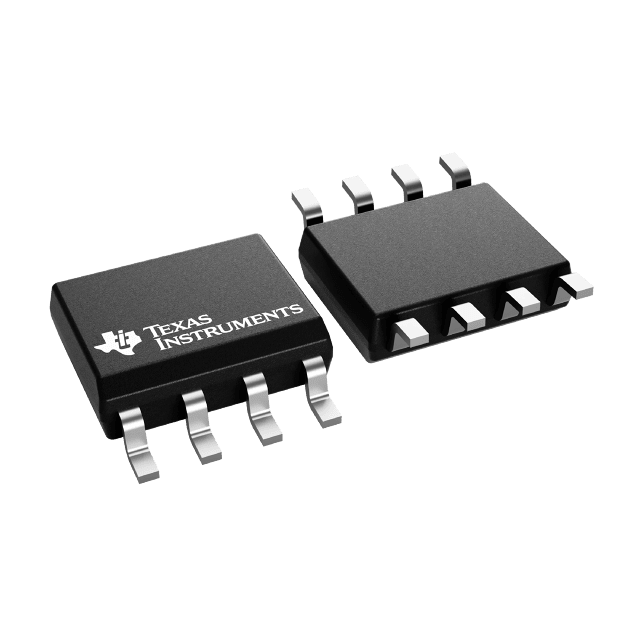

LM46002AQPWPRQ1 gói HTSSOP16 mạch tích hợp IC chip mới ban đầu tại chỗ linh kiện điện tử

Thuộc tính sản phẩm

| KIỂU | SỰ MIÊU TẢ |

| Loại | Mạch tích hợp (IC) |

| người bán | Dụng cụ Texas |

| Loạt | Ô tô, AEC-Q100, SIMPLE SWITCHER® |

| Bưu kiện | Băng & Cuộn (TR) Cắt băng (CT) Digi-Reel® |

| SPQ | 2000T&R |

| trạng thái sản phẩm | Tích cực |

| Chức năng | Bước xuống |

| Cấu hình đầu ra | Tích cực |

| Cấu trúc liên kết | Cái xô |

| Loại đầu ra | có thể điều chỉnh |

| Số lượng đầu ra | 1 |

| Điện áp - Đầu vào (Tối thiểu) | 3,5V |

| Điện áp - Đầu vào (Tối đa) | 60V |

| Điện áp - Đầu ra (Tối thiểu/Cố định) | 1V |

| Điện áp - Đầu ra (Tối đa) | 28V |

| Sản lượng hiện tại | 2A |

| Tần số - Chuyển mạch | 200kHz ~ 2,2 MHz |

| Bộ chỉnh lưu đồng bộ | Đúng |

| Nhiệt độ hoạt động | -40°C ~ 125°C (TJ) |

| Kiểu lắp | Gắn bề mặt |

| Gói / Thùng | Tấm lót lộ ra 16-TSSOP (0,173", chiều rộng 4,40mm) |

| Gói thiết bị của nhà cung cấp | 16-HTSSOP |

| Số sản phẩm cơ sở | LM46002 |

Quy trình sản xuất chíp

Quy trình chế tạo chip hoàn chỉnh bao gồm thiết kế chip, sản xuất tấm bán dẫn, đóng gói chip và kiểm tra chip, trong đó quy trình sản xuất tấm bán dẫn đặc biệt phức tạp.

Bước đầu tiên là thiết kế chip, dựa trên các yêu cầu thiết kế, chẳng hạn như mục tiêu chức năng, thông số kỹ thuật, bố trí mạch, cuộn dây và chi tiết, v.v. "Bản vẽ thiết kế" được tạo ra;mặt nạ ảnh được sản xuất trước theo quy định của chip.

②.Sản xuất wafer.

1. Tấm wafer silicon được cắt theo độ dày yêu cầu bằng máy cắt lát wafer.Tấm wafer càng mỏng thì chi phí sản xuất càng thấp nhưng quy trình càng đòi hỏi khắt khe.

2. phủ lên bề mặt tấm bán dẫn một lớp màng quang điện, giúp cải thiện khả năng chống oxy hóa và nhiệt độ của tấm bán dẫn.

3. Quá trình phát triển và khắc quang khắc wafer sử dụng các hóa chất nhạy cảm với tia UV, tức là chúng trở nên mềm hơn khi tiếp xúc với tia UV.Hình dạng của chip có thể thu được bằng cách kiểm soát vị trí của mặt nạ.Một chất quang dẫn được phủ lên tấm wafer silicon để nó sẽ hòa tan khi tiếp xúc với tia UV.Điều này được thực hiện bằng cách đắp phần đầu tiên của mặt nạ sao cho phần tiếp xúc với tia UV bị hòa tan và phần hòa tan này sau đó có thể được rửa sạch bằng dung môi.Phần hòa tan này sau đó có thể được rửa sạch bằng dung môi.Phần còn lại sau đó được tạo hình giống như chất quang dẫn, tạo cho chúng ta lớp silica mong muốn.

4. Tiêm ion.Sử dụng máy khắc, bẫy N và P được khắc vào silicon trần và các ion được bơm vào để tạo thành điểm nối PN (cổng logic);lớp kim loại phía trên sau đó được kết nối với mạch bằng lượng mưa thời tiết hóa học và vật lý.

5. Kiểm tra wafer Sau các quá trình trên, một mạng xúc xắc được hình thành trên wafer.Các đặc tính điện của từng khuôn được kiểm tra bằng cách sử dụng thử nghiệm chốt.

③.Bao bì chip

Tấm wafer thành phẩm được cố định, gắn vào các chốt và được đóng thành nhiều gói khác nhau tùy theo nhu cầu.Ví dụ: DIP, QFP, PLCC, QFN, v.v.Điều này chủ yếu được xác định bởi thói quen sử dụng ứng dụng của người dùng, môi trường ứng dụng, tình hình thị trường và các yếu tố ngoại vi khác.

④.Kiểm tra chip

Quá trình cuối cùng của sản xuất chip là thử nghiệm thành phẩm, có thể được chia thành thử nghiệm chung và thử nghiệm đặc biệt, trước đây là kiểm tra các đặc tính điện của chip sau khi đóng gói trong các môi trường khác nhau, chẳng hạn như mức tiêu thụ điện năng, tốc độ hoạt động, điện trở, v.v. Sau khi thử nghiệm, các con chip được phân loại thành các loại khác nhau tùy theo đặc tính điện của chúng.Thử nghiệm đặc biệt dựa trên các thông số kỹ thuật theo nhu cầu đặc biệt của khách hàng và một số chip có thông số kỹ thuật và chủng loại tương tự được thử nghiệm để xem liệu chúng có thể đáp ứng nhu cầu đặc biệt của khách hàng hay không, để quyết định xem có nên thiết kế chip đặc biệt cho khách hàng hay không.Các sản phẩm đã vượt qua bài kiểm tra chung sẽ được dán nhãn thông số kỹ thuật, số model, ngày xuất xưởng và được đóng gói trước khi rời khỏi nhà máy.Những con chip không vượt qua bài kiểm tra được phân loại là hạ cấp hoặc bị từ chối tùy thuộc vào các thông số mà chúng đạt được.

.png)