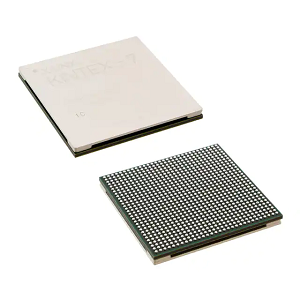

XC7K420T-2FFG901I – Mạch tích hợp, Mảng cổng lập trình dạng nhúng, dạng trường

Thuộc tính sản phẩm

| KIỂU | MINH HỌA |

| loại | Mạch tích hợp (IC)Đã nhúng Mảng cổng lập trình được dạng trường (FPGA) |

| nhà chế tạo | AMD |

| loạt | Kintex®-7 |

| bọc | cái mâm |

| Trạng thái sản phẩm | Tích cực |

| DigiKey có thể lập trình | Chưa xác minh |

| Số phòng thí nghiệm/câu lạc bộ | 32575 |

| Số phần tử/đơn vị logic | 416960 |

| Tổng số bit RAM | 30781440 |

| Số lượng I/O | 380 |

| Điện áp - Nguồn điện | 0,97V ~ 1,03V |

| Loại cài đặt | Loại keo dán bề mặt |

| Nhiệt độ hoạt động | -40°C ~ 100°C (TJ) |

| Trọn gói/Nhà ở | 900-BBGA, FCBGA |

| Đóng gói thành phần nhà cung cấp | 901-FCBGA (31x31) |

| Mã số sản phẩm | XC7K420 |

| KIỂU | MINH HỌA |

| loại | Mạch tích hợp (IC)Đã nhúng |

| nhà chế tạo | AMD |

| loạt | Kintex®-7 |

| bọc | cái mâm |

| Trạng thái sản phẩm | Tích cực |

| DigiKey có thể lập trình | Chưa xác minh |

| Số phòng thí nghiệm/câu lạc bộ | 32575 |

| Số phần tử/đơn vị logic | 416960 |

| Tổng số bit RAM | 30781440 |

| Số lượng I/O | 380 |

| Điện áp - Nguồn điện | 0,97V ~ 1,03V |

| Loại cài đặt | Loại keo dán bề mặt |

| Nhiệt độ hoạt động | -40°C ~ 100°C (TJ) |

| Trọn gói/Nhà ở | 900-BBGA, FCBGA |

| Đóng gói thành phần nhà cung cấp | 901-FCBGA (31x31) |

| Mã số sản phẩm | XC7K420 |

FPGA

Thuận lợi

Ưu điểm của FPGA như sau:

(1) FPGA bao gồm các tài nguyên phần cứng như ô logic, RAM, bộ nhân, v.v. Bằng cách tổ chức các tài nguyên phần cứng này một cách hợp lý, các mạch phần cứng như bộ nhân, thanh ghi, bộ tạo địa chỉ, v.v. có thể được triển khai.

(2) FPGA có thể được thiết kế bằng cách sử dụng sơ đồ khối hoặc Verilog HDL, từ các mạch cổng đơn giản đến mạch FIR hoặc FFT.

(3) FPGA có thể được lập trình lại vô hạn, tải giải pháp thiết kế mới chỉ trong vài trăm mili giây, sử dụng cấu hình lại để giảm chi phí phần cứng.

(4) Tần số hoạt động của FPGA được xác định bởi chip FPGA cũng như thiết kế và có thể được sửa đổi hoặc thay thế bằng chip nhanh hơn để đáp ứng các yêu cầu khắt khe nhất định (mặc dù, tất nhiên, tần số hoạt động không phải là giới hạn và có thể được tăng lên nhưng bị chi phối bởi các quy trình IC hiện tại và các yếu tố khác).

Nhược điểm

Nhược điểm của FPGA như sau:

(1) FPGA dựa vào việc triển khai phần cứng cho tất cả các chức năng và không thể thực hiện các hoạt động như phân nhánh các bước nhảy có điều kiện.

(2) FPGA chỉ có thể thực hiện các hoạt động điểm cố định.

Tóm lại: FPGA dựa vào phần cứng để thực hiện tất cả các chức năng và có thể so sánh với các chip chuyên dụng về tốc độ, nhưng có một khoảng cách lớn về tính linh hoạt trong thiết kế so với các bộ xử lý đa năng.

Ngôn ngữ thiết kế và nền tảng

Các thiết bị logic lập trình được là các thiết bị mang phần cứng cụ thể hóa các chức năng đã thiết lập và thông số kỹ thuật của các ứng dụng điện tử thông qua công nghệ EDA.FPGA, với tư cách là một trong những thiết bị chính thực hiện đường dẫn này, hướng trực tiếp đến người dùng, cực kỳ linh hoạt và linh hoạt, dễ sử dụng, nhanh chóng kiểm tra và triển khai trong phần cứng.

Ngôn ngữ mô tả phần cứng (HDL) là ngôn ngữ dùng để thiết kế hệ thống logic kỹ thuật số và mô tả các mạch kỹ thuật số, các ngôn ngữ chính được sử dụng phổ biến là VHDL, Verilog HDL, System Verilog và System C.

Là ngôn ngữ mô tả phần cứng toàn diện, Ngôn ngữ mô tả phần cứng mạch tích hợp tốc độ rất cao (VHDL) có đặc điểm là độc lập với mạch phần cứng cụ thể và độc lập với nền tảng thiết kế, với ưu điểm là khả năng mô tả phạm vi rộng, không phụ thuộc vào các thiết bị cụ thể và khả năng mô tả thiết kế logic điều khiển phức tạp bằng một mã chặt chẽ và ngắn gọn, v.v. Nó được nhiều công ty EDA hỗ trợ và đã được sử dụng rộng rãi trong lĩnh vực thiết kế điện tử.sử dụng rộng rãi.

VHDL là ngôn ngữ cấp cao để thiết kế mạch và so với các ngôn ngữ mô tả phần cứng khác, nó có đặc điểm là ngôn ngữ đơn giản, linh hoạt và độc lập với thiết kế thiết bị, khiến nó trở thành ngôn ngữ mô tả phần cứng phổ biến cho công nghệ EDA và làm cho công nghệ EDA trở nên phổ biến hơn. có thể tiếp cận được với các nhà thiết kế.

Verilog HDL là ngôn ngữ mô tả phần cứng được sử dụng rộng rãi, có thể được sử dụng trong nhiều giai đoạn của quy trình thiết kế phần cứng, bao gồm mô hình hóa, tổng hợp và mô phỏng.

Verilog HDL Ưu điểm: tương tự C, dễ học và linh hoạt.Trường hợp nhạy cảm.Ưu điểm trong việc viết kích thích và mô hình hóa.Nhược điểm: không thể phát hiện được nhiều lỗi tại thời điểm biên dịch.

Ưu điểm của VHDL: Cú pháp chặt chẽ, phân cấp rõ ràng.Nhược điểm: thời gian làm quen lâu, chưa linh hoạt.

Phần mềm Quartus_II là môi trường thiết kế đa nền tảng hoàn chỉnh do Altera phát triển, có thể đáp ứng nhu cầu thiết kế của nhiều loại FPGA và CPLD khác nhau, đồng thời là môi trường toàn diện cho thiết kế hệ thống lập trình trên chip.

Vivado Design Suite, một môi trường thiết kế tích hợp do nhà cung cấp FPGA Xilinx phát hành vào năm 2012. Nó bao gồm môi trường thiết kế tích hợp cao và thế hệ công cụ mới từ cấp độ hệ thống đến cấp độ IC, tất cả đều được xây dựng trên mô hình dữ liệu có thể mở rộng chung và môi trường gỡ lỗi chung.Xilinx Vivado Design Suite cung cấp lõi IP FIFO có thể dễ dàng áp dụng cho các thiết kế.